圍繞“55611”鍛造“實力高新” 新興能源技術研發的路徑與展望

近年來,高新技術產業園區(如“高新”)以“55611”規劃為引領,致力于打造具有核心競爭力的“實力高新”。其中,新興能源技術研發成為推動園區高質量發展的重要引擎。本文將圍繞“55611”戰略框架,探討新興能源技術研發在其中的關鍵作用、發展路徑及未來展望。

一、“55611”戰略與新興能源技術的定位

“55611”是高新區產業發展的核心戰略,通常涵蓋5大重點產業、5大創新平臺、6大發展路徑、1個核心目標及1個保障體系。新興能源技術作為5大重點產業之一,聚焦太陽能、風能、氫能、儲能及智慧能源等前沿領域,旨在通過技術創新驅動綠色低碳轉型,為“實力高新”注入強勁動力。

二、新興能源技術研發的關鍵領域

- 太陽能技術:重點發展高效光伏電池、光熱綜合利用及光伏建筑一體化(BIPV),提升能源轉換效率與應用廣度。

- 風能技術:推進大型風機智能控制、海上風電及低風速區域適用技術,增強風能資源開發利用能力。

- 氫能技術:加強制氫、儲運及燃料電池研發,構建“制-儲-用”一體化氫能產業鏈。

- 儲能技術:發展鋰離子電池、鈉硫電池及壓縮空氣儲能等,解決能源間歇性問題,保障電網穩定。

- 智慧能源系統:依托物聯網、大數據與人工智能,實現能源供需智能匹配與優化調度。

三、發展路徑與創新舉措

為實現“55611”目標,高新區需采取以下路徑:

- 強化產學研合作:聯合高校、科研機構與企業,共建能源技術實驗室與中試基地,加速成果轉化。

- 推動政策支持:制定資金補貼、稅收優惠及綠色金融政策,降低研發成本,吸引社會資本投入。

- 構建產業生態:培育能源技術龍頭企業與中小企業集群,形成“研發-制造-服務”全鏈條協同。

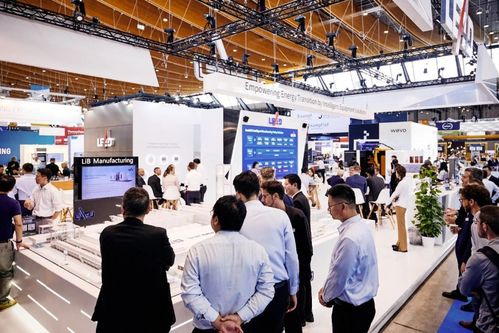

- 深化國際合作:引進海外先進技術與管理經驗,參與全球能源治理,提升國際競爭力。

四、挑戰與未來展望

盡管新興能源技術研發前景廣闊,但仍面臨核心技術瓶頸、成本過高及市場接受度等挑戰。未來,高新區需以“55611”為藍圖,持續加大研發投入,推動能源技術與數字經濟、高端制造融合,力爭在2030年前實現能源自給率大幅提升,碳排放顯著下降,最終建成綠色、智能、高效的“實力高新”樣板。

新興能源技術研發是“55611”戰略不可或缺的一環。通過聚焦創新、優化生態,高新區必將鍛造出更具韌性與影響力的“實力高新”,為國家能源安全與碳中和目標貢獻力量。

如若轉載,請注明出處:http://www.bhysys.cn/product/5.html

更新時間:2026-03-09 23:46:54